## PROCEEDINGS OF SPIE

SPIEDigitalLibrary.org/conference-proceedings-of-spie

# Ruthenium direct etch scatterometry solution for self-aligning semi-damascene

Paolillo, Sara, Moussa, Alain, Murdoch, Gayle, Lazzarino, Frederic, Charley, Anne-Laure, et al.

Sara Paolillo, Alain Moussa, Gayle Murdoch, Frederic Lazzarino, Anne-Laure Charley, Philippe Leray, Joey Hung, Roy Koret, Shay Wolfling, Avron Ger, "Ruthenium direct etch scatterometry solution for self-aligning semi-damascene," Proc. SPIE 11325, Metrology, Inspection, and Process Control for Microlithography XXXIV, 1132519 (12 May 2020); doi: 10.1117/12.2550366

Event: SPIE Advanced Lithography, 2020, San Jose, California, United States

### Ruthenium Direct Etch Scatterometry Solution for Self-aligning Semidamascene

Sara Paolillo<sup>1</sup>, Alain Moussa<sup>1</sup>, Gayle Murdoch<sup>1</sup>, Frederic Lazzarino<sup>1</sup>, Anne-Laure Charley<sup>1</sup>, Phillipe Leray<sup>1</sup>,

Joey Hung<sup>2</sup>, Roy Koret<sup>3</sup>, Shay Wolfling<sup>3</sup>, Avron Ger<sup>3</sup>

<sup>1</sup> IMEC, Kapeldreef 75, 3001 Heverlee, Belgium

#### **ABSTRACT**

Beyond the 5nm technology node, interconnect scaling has an impact on metal material selection: usage of copper may hit a limit with respect to resistance and reliability performance [1]. Thickness of barrier and liner (required for copper) cannot be reduced further, meaning that trench width reduction will have a negative effect on the relative copper volume. Grain boundary scattering increases as well, which in turn further increases resistivity and resistance. One of the best alternatives is Ruthenium (Ru), but dual-damascene processing is difficult with Ru (requires improvements in Ru filling of narrow high aspect ratio trenches and in Ru CMP selectivity and defects). So, a Back End of Line (BEOL) material change may require a move to a semi-damascene integration with direct Ruthenium metal etch [2].

This shift from a well-known dual-damascene flow, based on metal CMP, to a semi-damascene flow, based on metal etch integration, will require a new set of metrology capabilities, which are studied in this paper.

In the current study, Scatterometry is widely used in all semi-damascene process steps to monitor both dimensional and material properties. Important measured parameters include thickness, full profile details, grain size, and roughness of metal lines—all parameters that are required for feedback and in-line process control. We will describe how these parameters can be monitored using a single Scatterometry metrology system.

The semi-damascene process development described in this paper exploits EUV lithography at a critical dimension (CD) of 16 nm and 32 nm pitch and includes the optimization of the following process steps:

- 1. Metal deposition techniques: ALD and PVD, with a wide range of metal thickness.

- 2. Anneal, affecting grain size.

- 3. Etch process, for optimal metal line profile and roughness.

The Scatterometry results were evaluated and verified by reference techniques such as CDSEM, and HAADF-STEM.

The goal of the process optimization was Ru resistivity and resistance. In-line Scatterometry was shown to accurately predict the resistance of the Ru lines — parameter that is measured at the end of the processing, and is affected by all processes, including deposition, annealing, and etch. Prediction was carried out by a machine learning algorithm, based on an E-test, combining the contribution of all three process steps into a single output, at the post-etch measurement phase.

Keywords: Interconnect, Sub-5nm, Semi-damascene, Ruthenium, Scatterometry, Line resistance.

Nova Measuring Instruments, Bruno-Paul Haus Moritzburger Weg 67, 01109 Dresden, Germany

<sup>&</sup>lt;sup>3</sup> Nova Measuring Instruments, LTD, P.O. Box 266, Weizmann Science Park, Rehovot 76100, Israel

#### 1. INTRODUCTION

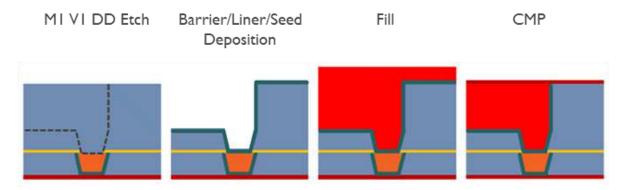

In today's BEOL processing for advance nodes, such as 7nm, dual-damascene is still the selected technique. The dual-damascene technique, with copper interconnect, which was introduced in the late 90s, consists of the following process steps: interconnect patterning, etch of Inter-Layer-Dielectric (ILD), and copper plating (Figure 1). This last step began reaching its physical and device performance limitations, due to the continuing shrinking of critical dimensions. The creation of a void-less connection line is a physical limitation, due to the narrow trench, and the required liner, barrier, and Cu seed depositions, which leave a minimal space for the Cu plating. Moreover, the scaling limitation of the Cu diffusion barrier contributes to the overall wire resistance increase. The line-to-line capacitance increases when moving to higher aspect ratio lines, also contributing to reduced interconnection performance.

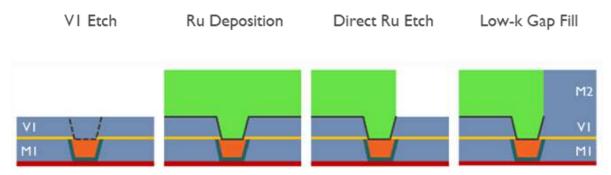

Semi-damascene is an alternative technique capable of solving each of these challenges. This technique has a different process flow, starting with patterning the vias in a dielectric layer and filling them with a metal deposition. Metal is then patterned by direct etch. With this scheme, there is no need for a diffusion barrier and liner. In addition, this process flow enables the insertion of air gaps between the Ruthenium lines, thereby lowering the line-to-line capacitance. Regarding material selection, Ruthenium is a leading candidate. It has low bulk resistivity, is easy to pattern with existing etch reactors, and it is easy to clean from the etch chamber. It has a high melting point and requires no diffusion barriers [3].

Figure 1: Dual-damascene standard flow. Main process segments are (in chronological order)—Lithography, Dielectric Etch, Metallization.

Figure 2: Semi-damascene standard flow. Main process segments are (in chronological order)—Metallization, Lithography, Metal Etch.

#### 2. DIRECT METAL ETCH PROCESS STEPS AND METROLOGY NEEDS

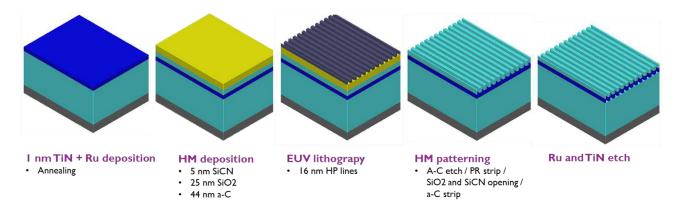

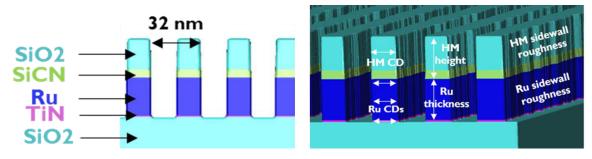

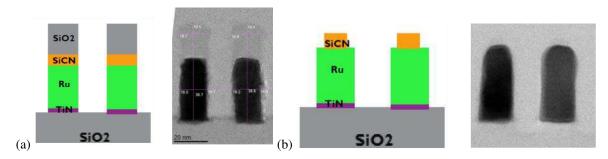

In our work we use a single-level damascene process to reach the target step of post metal etch. The process starts with a deposition of 1nm TiN adhesion layer on a thick SiO2 blanket layer, and the deposition of a Ruthenium layer with varying thicknesses of 24nm, 36nm, and 48nm. PVD Ruthenium is used for most of the wafers, while a few undergo ALD Ruthenium. The deposition is followed by an annealing split at 0 C°, 420 C°, and 600 C°. The next step is a hard mask deposition, which consists of 5nm SiCN, 25nm SiO2, and 44nm a-C. EUV lithography is exploited to target features at 32 nm pitch, with 16nm line/space. The pattern is transferred first in the a-C layer and then etched into the hard mask layers(SiO2 and SiCN). The final step includes etching into the Ruthenium and TiN layers (Figure 3). The resulting Ruthenium lines have distinctive properties, which are due to the split conditions (Table 1). For this innovative direct Ruthenium etch, it is critical to characterize all the key geometrical and material properties. In this work we examine the Scatterometry (also known as OCD) to accurately measure all key parameters of the Ruthenium array, such as: Ruthenium height, Ruthenium top, middle, and bottom CDs, the hard mask height and CD, the Ruthenium and hard mask side-wall roughness, and the ability to predict the Ruthenium line resistance, via machine learning, using electrical measurements, at a subsequent step (Figure 4). The OCD tool uses multi-channel measurements, derived from normal and oblique channels, in a broadband wavelength from UV to IR. All OCD geometry properties' results are matched to a known reference measurement such as CDSEM (for top CD and roughness), and TEM (for remaining dimensional parameters). CDSEM measurements are conducted on all wafers under test, and include a full wafer map sampling for CD, with 50 dies per wafer, to perform a PSD analysis, based on IMEC roughness protocol [4].

Figure 3: Direct Ruthenium Etch—single level damascene process flow (used for this work)

Figure 4: Post-Ruthenium etch geometry, and materials under study. Key metrology target parameters are illustrated in a 3D view

Table 1: Process flow design of experiment, and split conditions effect on Ruthenium material properties, and dimensions

| Process Step/Method  | Design of Experiment | Split Effect                  |

|----------------------|----------------------|-------------------------------|

| Deposition technique | ALD, PVD             | Ruthenium material properties |

| Deposition thickness | 24nm, 36nm, 48nm     | Aspect ratio                  |

| Annealing            | 0 °C, 420 °C, 600 °C | Ruthenium grain size          |

| Etch technique       | Type#1, Type#2       | Ruthenium line geometry       |

#### 3. RESULTS

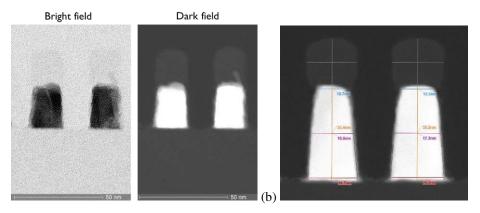

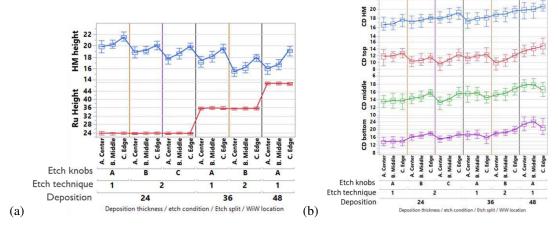

We have chosen to use dark field STEM images (High-Angle Annular Dark-Field imaging (HAADF)), which can extract all required key parameters in a single image technique, as compared to the bright field STEM, which can only accurately measure the Ruthenium shape (Figure 5). All samples and key parameter measurements were carried out in an automated mode. The multiple split-condition effects can be seen in the TEM results for the six target parameters. Six wafers were analyzed by this technique, sampling 3 dies per wafer, and 40-60 lines were analyzed per die, to obtain a significant statistic, with minimal noise, and can be seen in the error bars in these charts (Figure 6).

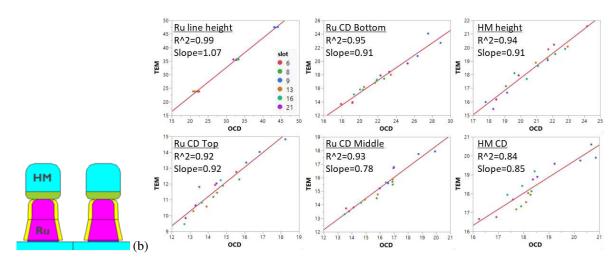

The OCD 2D array model was created based on these TEM images. The model's material characterization was performed using the previous deposition steps. Using a unique algorithm that optimizes accuracy performance, the OCD can provide a good matching performance for most of the key parameters (Figure 7).

Figure 5: TEM cross-section image of direct-Ruthenium etch. (a) Bright field vs. dark field TEM image are examined. Dark-field technique was selected to accurately measure both the Ruthenium and SiO2 hard mask properties. (b) An example of dark-field automated TEM measurement for all key target parameters.

Figure 6: TEM measurement results. Measurements collected for 6 wafers, 3 dies (center, middle, and edge of wafer), 40-60 lines measured at each target. Results show the effect of the different DoE split conditions at deposition and etch process steps.

Figure 7: (a) OCD physical model geometrical description. Yellow line represents the edge roughness. (b) OCD results compared to the TEM reference. OCD can provide most key parameters with high accuracy.

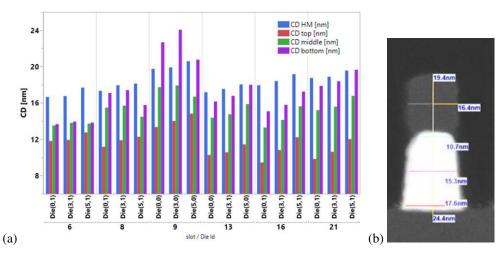

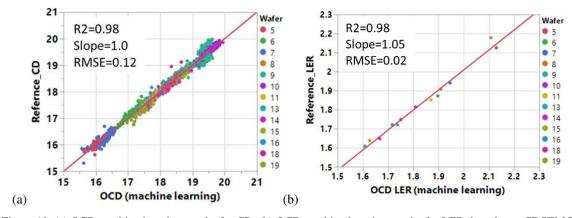

Another objective of the Ruthenium etch work was to examine which method could provide an accurate in-line measurement of CD. We examined the TEM results (Figure 8) for the different CDs from hard mask and Ruthenium. For most wafers and dies measured by TEM, it can be clearly seen that a hard mask CD is larger than all Ruthenium CDs. Thus, CDSEM top view measurement cannot directly measure the key property of Ruthenium CD and Line Edge Roughness (LER) at the post-Ruthenium etch step. An alternative approach for measuring these parameters is to use OCD machine learning. In order to obtain a large data set, which is required for machine learning training and crossvalidation, additional CDSEM measurements were obtained at the post-hard mask removal. This additional process step is not part of the semi-damascene process flow, but it allows us to remove the SiO2 hard mask, without affecting the Ruthenium line, and be able of directly measuring the Ruthenium CD and LER by CDSEM. A representative TEM image of the post-hard mask removal step is seen in Figure 9. A machine learning algorithm is used to train the OCD spectra with the appropriate CDSEM sampling. The machine learning performance on a wafer set, which is not included in the training set, shows a good performance matching using this technique (Figure 10). The CDSEM LER results show a large within-wafer distribution. This LER distribution is the result of CDSEM noise. To obtain a valid CDSEM LER value, the (IMEC) protocol requires the averaging of at least 50 CDSEM images [4]. For all wafers we compare the wafer's average machine learning prediction to the average CDSEM LER result. Performance matching shows that OCD is sensitive to both CD and LER (Figure 10).

Figure 8: Based on TEM images, we can learn that for the Ruthenium etch, the hard-mask CD is larger than Ruthenium top, middle, and bottom CDs, for most wafers and dies.

Figure 9: (a) OCD measurements performed at the post-Ruthenium etch. (b) CDSEM measurements performed at the post hard-mask removal stage, in order to measure Ruthenium parameters. This is not part of the semi-damascene process flow and is suggested only for wafers selected for the OCD machine learning training set.

Figure 10: (a) OCD machine learning results for CD. (b) OCD machine learning results for LER, based on a CDSEM PSD analysis. Due to a large PSD results distribution within each wafer, resulting from CDSEM measurement noise (0.26nm), we present an average value per wafer.

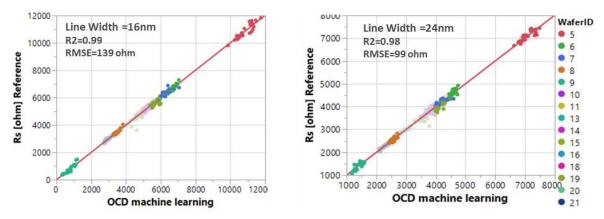

Using the machine learning approach, we can also predict the Ruthenium line's electrical performance. Two electrical targets were measured; the first one with a line CD at a nominal value of 16nm, and the second one with a larger CD of 24nm. The electrical measurement was conducted post the Ruthenium etch step. We used the same OCD target

measurements and by using machine learning on a training wafers subset, we were able to show the prediction capability for all other wafers that were not part of the training set. The high level of performance matching shows that we can use OCD at the target process step to predict what will be the electrical resistance of the lines.

Figure 11: OCD machine learning results for resistance measurements, obtained from E-test targets of line width 16nm, and 24nm. OCD spectra was collected using a metrology box with a 16nm nominal line width.

#### 4. CONCLUSIONS

In our work we have described an emerging interconnect technology named semi-damascene which has the potential of replacing the current dual-damascene flow. We showed that OCD metrology is capable, by making use of physical modeling and machine learning training, of answering both development needs. It measures all geometrical target parameters and provides in-line control needs such as CD, roughness, and resistance, and enables excellent prediction capabilities. We conclude by stating that physical modeling and machine learning are complementary OCD methods, that can serve both R&D and production requirements for Ruthenium direct etch.

#### **ACKNOWLEDGEMENT**

I would like to give special recognition to IMEC integration, metrology, and TEM owners for their support in wafer processing and reference metrology measurements and analysis. We would also wish to indicate that this project has received funding from the ECSEL Joint Undertaking (JU), under grant agreement No. 826589. The JU receives support from the European Union's Horizon 2020 research and innovation program, and from Netherlands, Belgium, Germany, France, Italy, Austria, Hungary, Romania, Sweden and Israel.

#### REFERENCES

- [1] Zhang, X., et al., "Ruthenium interconnect resistivity and reliability at 48 nm pitch," 2016 IEEE International Interconnect Technology Conference/Advanced Metallization Conference (IITC/AMC), San Jose, CA, 2016, pp. 31-33.

- [2] Paolillo, S., "Direct metal etch of ruthenium for advanced interconnect", Journal of Vacuum Science & Technology B 36, 03E103 (2018)

- [3] Adelmann, C., et al., "Alternative Metals: from ab initio Screening to Calibrated Narrow Line Models", IEEE IITC 2018.

- [4] Lorusso, G.F., et al., "Need for LWR metrology standardization: the imec roughness protocol", J. Micro/Nanolithography, MEMS and MOEMS 17(4), 041009 (2018).